C++内存模型性能对比分析

发布于2025-10-09 阅读(0)

发布于2025-10-09 阅读(0)

扫一扫,手机访问

C++内存序性能开销从低到高为relaxed < acquire/release < seq_cst,因对内存重排和可见性的限制逐步增强,导致编译器和CPU需插入更多内存屏障,影响优化和执行效率。

C++内存模型中不同内存序的开销确实差异巨大,这直接关系到CPU和编译器为维护内存一致性与操作顺序而付出的代价。简单来说,从memory_order_relaxed到memory_order_seq_cst,性能开销是逐步增加的,因为它们对内存操作的重排限制和可见性保证强度不同,最终体现为更少的优化机会和更多的底层同步指令(如内存屏障)。

解决方案

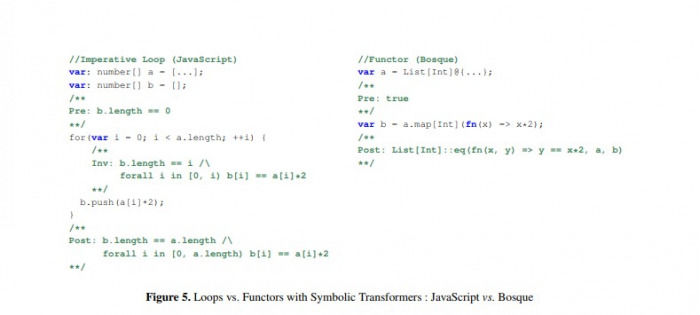

理解C++内存模型的性能差异,首先要深入到硬件层面。CPU为了提高执行效率,会进行指令重排,内存子系统也会有写缓冲、缓存一致性协议等机制。编译器同样为了优化,会重排指令。在单线程环境下,这些重排是透明且无害的,但在多线程中,它们可能导致数据竞争和不确定行为。C++内存模型和原子操作就是为了在多线程环境下,在性能与正确性之间找到平衡点,通过不同的内存序来明确告诉编译器和CPU,哪些重排是被允许的,哪些是必须禁止的。

memory_order_relaxed是最宽松的内存序。它只保证原子操作本身的原子性,不提供任何跨线程的同步或排序保证。这意味着,一个线程对relaxed原子变量的写入,可能在另一个线程观察到之前,其它的非原子操作已经被观察到。CPU和编译器可以最大限度地自由重排,因此它的开销最小,通常就是一条原子指令的开销,比如X86上的lock add或mov指令,没有额外的内存屏障。

memory_order_acquire和memory_order_release构成了一对屏障。acquire操作会阻止它之后的读写操作被重排到它之前,而release操作会阻止它之前的读写操作被重排到它之后。它们协同工作,通常用于实现生产者-消费者模型:生产者在release一个数据后,消费者在acquire这个数据时,能保证看到release之前的所有操作结果。这种屏障的开销通常是中等的,它会在关键点插入CPU内存屏障(如X86上的sfence/lfence或ARM上的dmb指令),确保内存操作的可见性和顺序性。这些屏障会强制刷新写缓冲,或者等待某些内存操作完成,这比relaxed操作要慢,但比seq_cst通常要快。

memory_order_seq_cst(顺序一致性)是最严格的内存序,也是默认的内存序。它不仅保证原子操作的原子性,还保证所有seq_cst操作在所有线程中都以单一的、全局一致的顺序执行。这意味着,任何线程看到的seq_cst操作的顺序,都必须与其他所有线程看到的顺序一致。为了实现这种强保证,编译器和CPU需要插入更强的内存屏障,通常是全能屏障(full fence,如X86上的mfence)。这些屏障的开销最大,因为它们不仅要阻止重排,还要确保所有内存操作对所有核心都可见,这可能涉及更复杂的缓存一致性协议交互,甚至在某些架构上,seq_cst的存储操作可能需要一个Read-Modify-Write(RMW)操作来确保全局顺序,即便它只是一个简单的写入。

因此,性能开销的差异,本质上就是CPU和编译器在维护特定内存顺序和可见性保证时,需要插入多少以及何种类型的内存屏障指令。屏障越强,对CPU流水线的阻塞就越大,对缓存一致性协议的介入就越多,自然开销就越大。

C++内存序(Memory Order)的本质是什么,它如何影响多线程程序的可见性与顺序性?

C++内存序,或者说memory_order,本质上是程序员与编译器和CPU之间的一种契约,用来明确多线程环境下内存操作的可见性和顺序性。它不是简单地控制“谁先看到谁的修改”,而是更精细地定义了内存操作(读、写、RMW)相对于其他内存操作的排序限制。这种契约是解决数据竞争和确保并发程序正确性的核心机制。

它主要通过两种方式影响多线程程序的行为:

- 可见性 (Visibility):当一个线程修改了某个内存位置,另一个线程何时能够“看到”这个修改。没有适当的内存序,一个线程的修改可能长时间对其他线程不可见,因为数据可能还在本地CPU缓存或写缓冲中。

acquire和release内存序通过强制刷新或同步缓存,确保了特定内存区域的修改能够及时地被其他线程观察到。例如,release操作确保其之前的写操作对其他线程的acquire操作可见。 - 顺序性 (Ordering):一个线程内的多个内存操作,在实际执行时,其顺序是否可以被编译器或CPU重排。重排是为了提高性能,但如果重排打破了多线程间的逻辑依赖,就会导致错误。内存序通过在关键点插入内存屏障,来限制这种重排。

relaxed不提供任何顺序保证,只保证操作本身的原子性。acquire保证其后的内存操作不会被重排到acquire之前。release保证其前的内存操作不会被重排到release之后。seq_cst则提供最强的顺序保证,确保所有seq_cst操作在所有线程中都以相同的总顺序出现,这意味着它阻止了几乎所有可能破坏这种全局顺序的重排。

举个例子,假设线程A写入一个数据data,然后设置一个标志flag。线程B循环检查flag,一旦flag为真,就读取data。如果flag的设置和读取都是relaxed,那么线程B可能先看到flag为真,但读取到的data却是旧值,因为写入data的操作可能被重排到flag设置之后,或者data的修改还没有刷新到主存被线程B看到。但如果flag的设置是release,读取是acquire,那么线程B一旦看到flag为真,就必然能看到data的最新值,因为release确保了data的写入发生在flag设置之前并可见,而acquire确保了读取data的操作发生在flag读取之后。这就是内存序如何通过影响可见性和顺序性来确保多线程程序的正确性。

不同C++内存序的性能开销具体体现在哪里?以relaxed、acquire/release和seq_cst为例。

不同C++内存序的性能开销,主要体现在它们在底层硬件层面(CPU和内存控制器)以及编译层面(编译器优化)所引入的额外工作量。这并非一个简单的线性关系,而是与具体的CPU架构、缓存层次结构、以及系统负载都有关系。

memory_order_relaxed(最轻量级)- 开销体现: 它的开销几乎等同于一个普通的非原子操作,但需要保证原子性。在X86架构上,许多单指令的原子操作(如

mov或add操作到对齐的内存位置)本身就具有足够的原子性,编译器可能直接使用这些指令,或者在必要时加上lock前缀。这意味着,它不会引入额外的内存屏障指令。 - 实际影响: 性能损耗主要来自原子操作本身的指令周期。例如,一个

fetch_add(1, memory_order_relaxed)可能在X86上编译成一个lock add [mem], 1指令。这个lock前缀会锁定总线,确保操作的原子性,但不会像mfence那样阻止指令重排或强制刷新缓存。 - 适用场景: 适用于那些只需要原子性,而不需要任何跨线程同步或排序保证的场景,比如简单的计数器(最终一致性即可)、统计信息收集、或者在其他同步机制(如互斥锁)已经提供了足够同步保证的情况下,作为内部状态的原子更新。

- 开销体现: 它的开销几乎等同于一个普通的非原子操作,但需要保证原子性。在X86架构上,许多单指令的原子操作(如

memory_order_acquire/memory_order_release(中等开销)- 开销体现: 它们会引入内存屏障指令。

acquire操作通常对应一个读屏障或加载屏障,确保在它之后的读写操作不会被重排到它之前。它还可能涉及等待缓存行变为有效或刷新本地缓存。release操作通常对应一个写屏障或存储屏障,确保在它之前的读写操作不会被重排到它之后。它可能需要强制将写缓冲中的数据刷新到主存或共享缓存中。

- 实际影响: 这些屏障指令会阻塞CPU流水线,等待之前或之后的内存操作完成,这比

relaxed操作要慢。在X86上,由于其较强的内存模型,acquire可能不需要显式的指令(因为读操作本身就具有某种屏障特性),而release可能需要一个sfence指令。但在ARM等弱内存模型架构上,acquire和release通常都需要显式的dmb(Data Memory Barrier)指令,其开销更为显著。 - 缓存一致性:

acquire/release还会更频繁地与CPU的缓存一致性协议(如MESI)交互。release操作可能会导致缓存行从“修改”状态变为“共享”状态,并通知其他CPU核心其缓存行已失效,这可能引起缓存行在不同核心之间“弹跳”(cache line bouncing),从而增加延迟。 - 适用场景: 这是大多数无锁数据结构和同步原语(如自旋锁、信号量、生产者-消费者队列)的首选。它们提供了足够的同步保证,同时避免了

seq_cst的过高开销。

- 开销体现: 它们会引入内存屏障指令。

memory_order_seq_cst(最高开销)- 开销体现:

seq_cst通常会引入一个全能屏障(full fence),它既是读屏障也是写屏障,确保所有内存操作都严格按照程序顺序执行,并且对所有线程都可见。在X86上,这通常对应mfence指令。 - 实际影响:

mfence指令会清空所有写缓冲,并确保所有之前指令的内存效果都已完成,并且所有后续指令的内存效果都将在屏障之后发生。这是一个非常重的操作,会严重阻塞CPU流水线,导致显著的性能下降。更糟糕的是,seq_cst还要求所有seq_cst操作在所有线程中都以相同的全局顺序出现。在某些架构上,这可能需要更复杂的硬件机制,例如,seq_cst的存储操作可能需要一个RMW操作来确保其能参与到全局顺序中,即使它只是一个简单的写入。 - 全局同步: 它的高开销不仅在于单条指令的成本,还在于它强制了所有线程之间的全局同步点,这限制了CPU和编译器进行优化的空间。它可能导致更多的缓存行失效和重新加载,以及更长的等待时间。

- 适用场景: 当你对内存模型的细节不确定,或者需要最强的同步保证,例如,在某些复杂的算法中,需要确保所有线程都以完全相同的顺序观察到某些关键事件时。但通常情况下,它的开销过高,应尽量避免。

- 开销体现:

总的来说,性能开销的差异在于:relaxed是“只管自己”,acquire/release是“管好两边”,而seq_cst是“管好全局”。管的范围越大,需要付出的协调和等待成本就越高。

在实际项目中,如何权衡C++内存模型性能与正确性,并选择合适的内存序?

在实际项目中,权衡C++内存模型的性能与正确性,并选择合适的内存序,是一个需要深思熟虑且充满挑战的过程。这不仅仅是技术问题,更是一种工程哲学:我们是选择最安全但可能最慢的方式,还是冒险追求极致性能?我的经验是,除非有明确的性能瓶颈,否则宁愿牺牲一点性能来确保正确性。

从

memory_order_seq_cst开始(默认且最安全)- 思路: 如果你对C++内存模型没有深入理解,或者项目初期对并发行为的正确性要求极高,那么默认使用

memory_order_seq_cst是明智的选择。它是最保守的,提供最强的保证,能有效防止各种内存重排导致的并发bug。 - 权衡: 它的缺点是性能开销最大。但对于大多数并发场景,如果并发量不大,或者原子操作不是性能瓶颈,

seq_cst的开销可能是可接受的。 - 建议: 在不确定时,先用

seq_cst。确保功能正确后,再进行性能分析。

- 思路: 如果你对C++内存模型没有深入理解,或者项目初期对并发行为的正确性要求极高,那么默认使用

转向

memory_order_acquire/memory_order_release(性能与正确性的黄金平衡点)- 思路: 这是大多数无锁编程和并发数据结构的首选。当你需要构建生产者-消费者队列、自旋锁、简单的信号量或任何需要“发布-订阅”语义的场景时,

acquire/release是理想的选择。它们提供了足够的同步保证,确保了数据在逻辑上的“先行发生”(happens-before)关系,同时避免了seq_cst的全局同步开销。 - 权衡: 相较于

seq_cst,它们性能更好,但理解和正确使用它们需要对内存模型有更深的理解。一旦用错,可能导致难以调试的并发bug。 - 建议: 当你发现

seq_cst成为性能瓶颈,并且你能够清晰地定义数据依赖和同步点时,可以考虑使用acquire/release。这需要仔细分析程序的并发逻辑,确定哪些操作需要同步,以及它们之间的依赖关系。例如,在实现一个无锁队列时,push操作的写入需要用release,pop操作的读取需要用acquire。

- 思路: 这是大多数无锁编程和并发数据结构的首选。当你需要构建生产者-消费者队列、自旋锁、简单的信号量或任何需要“发布-订阅”语义的场景时,

谨慎使用

memory_order_relaxed(极致性能,但风险最高)- 思路: 只有当你明确知道某个原子操作仅仅需要原子性,而不需要任何排序或可见性保证,并且你已经通过其他机制(如互斥锁、其他

acquire/release操作)确保了必要的同步时,才考虑使用relaxed。 - 权衡: 性能开销最小,但它不提供任何内存顺序保证,这意味着编译器和CPU可以随意重排操作。如果误用,可能导致非常隐蔽且难以复现的bug。调试这类bug简直是噩梦。

- 建议: 仅用于以下场景:

- 计数器: 比如一个全局的统计计数器,最终一致性即可,不要求每个线程立即看到最新值。

- 非关键状态标志: 某个状态标志,其改变不需要立即影响其他线程的行为,或者其影响已经被其他更强的同步机制覆盖。

- 在其他同步机制内部: 作为更大同步结构(如互斥锁内部)的一部分,仅用于原子更新,而其同步性由外部结构保证。

- 重要提示: 使用

relaxed前,务必仔细阅读C++标准关于内存模型的章节,并进行彻底的测试(包括压力测试和使用ThreadSanitizer等工具)。

- 思路: 只有当你明确知道某个原子操作仅仅需要原子性,而不需要任何排序或可见性保证,并且你已经通过其他机制(如互斥锁、其他

额外的考量:

- CPU架构差异: 不同的CPU架构(X86、ARM、PowerPC等)有不同的内存模型。X86的内存模型相对较强,某些情况下

acquire/release可能不会引入显式的内存屏障指令(因为硬件已经提供了部分保证)。而ARM等弱内存模型架构则需要更多的显式屏障。这意味着,在X86上,acquire/release与seq_cst的性能差异可能不如在ARM上那么显著。在进行跨平台开发时,这一点尤为重要。 - 缓存行争用(Cache Line Contention): 即使是

relaxed操作,如果多个核心频繁读写同一个缓存行上的原子变量,也会因为缓存一致性协议(如MESI)导致缓存行在核心之间“弹跳”,从而产生显著的性能开销。这与内存序本身无关,而是硬件层面的物理限制。 - 代码可读性与维护性: 过度优化内存序可能会使代码变得难以理解和维护。在性能不是绝对瓶颈的情况下,优先选择更清晰、更易懂的

seq_cst或acquire/release。

我的个人观点是,C++内存模型是并发编程中最复杂、最容易出错的领域之一。不要为了微小的性能提升而贸然使用relaxed。通常,acquire/release是性能和正确性的最佳折衷点。只有在有明确的性能瓶颈,并且你对内存模型有极其深刻的理解和充分的测试覆盖时,才考虑进一步放宽内存序。否则,你省下的CPU周期,最终可能会以数倍的时间成本花在调试那些难以捉摸的并发bug上。

免责声明:正软商城发布此文仅为传递信息,不代表正软商城认同其观点或证实其描述。

产品推荐

-

售后无忧

立即购买>- DAEMON Tools Lite 10【序列号终身授权 + 中文版 + Win】

-

¥150.00

office旗舰店

-

售后无忧

立即购买>- DAEMON Tools Ultra 5【序列号终身授权 + 中文版 + Win】

-

¥198.00

office旗舰店

-

售后无忧

立即购买>- DAEMON Tools Pro 8【序列号终身授权 + 中文版 + Win】

-

¥189.00

office旗舰店

-

售后无忧

立即购买>- CorelDRAW X8 简体中文【标准版 + Win】

-

¥1788.00

office旗舰店

-

正版软件

正版软件

- 如何在 Java 中利用 Character.isWhitespace() 识别文本变量中肉眼不可见的控制字符

- Character.isWhitespace():它真能揪出所有“隐形”字符吗? 在文本处理中,我们常常需要清理那些看不见的“捣蛋鬼”——控制字符。很多开发者第一个想到的工具可能就是 Character.isWhitespace()。但这里有个关键认知需要厘清:这个方法并非检测所有不可见字符的万能钥

- 49分钟前 0

-

正版软件

正版软件

- Sublime实现多仓库Git版本控制中心_强化分支可视化与代码冲突解决方法

- Sublime Text 依赖 Sublime Merge 实现多仓库 Git 管理:官方 Git 插件仅封装 CLI、限单仓库操作;Sublime Merge 提供工作区、分支可视化、批量同步及三方冲突解决,需正确配置 git_binary 和 mergetool。 简单来说,Sublime Te

- 2小时前 13:54 0

-

正版软件

正版软件

- Composer镜像源白名单管理_加强内网安全性

- Composer镜像源白名单管理:从配置到安全的完整解读 Composer无镜像源白名单机制,本质是禁用默认源后显式声明可信仓库;需全局配置repo.packagist=false并严格定义repositories键名、type与https镜像URL,否则包发现失效或校验降级。 先明确一个核心概念:

- 2小时前 13:53 0

-

正版软件

正版软件

- Composer有什么性能瓶颈?分析大规模依赖安装延迟

- Composer有什么性能瓶颈?分析大规模依赖安装延迟 Composer install 卡在 Resolving dependencies 是 CPU 在暴力穷举 先澄清一个普遍的误解:当你看到 composer install 长时间卡在“Resolving dependencies”阶段,这通

- 2小时前 13:53 0

-

正版软件

正版软件

- VSCode运行代码怎么切换虚拟环境 VSCode选择conda环境运行

- VSCode中需同步配置解释器选择、终端激活和调试设置三者:先确保conda在PATH并运行conda init,再通过Python: Select Interpreter手动指定路径;启用python.terminal.activateEnvironment使终端自动激活;调试时须在launch.

- 2小时前 13:53 0

最新发布

-

1

1

-

2

2

-

3

3

- C语言中\n是什么意思?换行转义字符详解

- 238天前

-

4

- 探析Spring Boot框架的优点和特色

- 554天前

-

5

- 深入比较PyCharm社区版和专业版的功能

- 492天前

-

6

- 专家观点:谷歌是否会继续支持Golang的探讨

- 468天前

-

7

7

- Python实战教程:批量转换多种音乐格式

- 1100天前

-

8

- 如何在在线答题中实现试卷的自动批改和自动评分

- 928天前

-

9

9

- 解决Python安装失败的问题

- 478天前

相关推荐

- 如何在 Java 中利用 Character.isWhitespace() 识别文本变量中肉眼不可见的控制字符

- Sublime实现多仓库Git版本控制中心_强化分支可视化与代码冲突解决方法

- Composer镜像源白名单管理_加强内网安全性

- Composer有什么性能瓶颈?分析大规模依赖安装延迟

- VSCode运行代码怎么切换虚拟环境 VSCode选择conda环境运行

- 应对零日漏洞爆发:掌握Composer全局更新指令快速修复框架底层

- Composer怎么检查依赖安全漏洞_Composer审计插件使用说明

- VSCode怎么运行HTML网页 VSCode实时预览网页方法

- Sublime如何运行Python代码_Sublime配置Python开发环境方法

热门关注

-

- Xshell 6 简体中文

- ¥899.00-¥1149.00

-

- DaVinci Resolve Studio 16 简体中文

- ¥2550.00-¥2550.00

-

- Camtasia 2019 简体中文

- ¥689.00-¥689.00

-

- Luminar 3 简体中文

- ¥288.00-¥288.00

-

- Apowersoft 录屏王 简体中文

- ¥129.00-¥339.00