台积电更新 SoIC 3D 芯片封装堆叠技术路线图:2029 年互连间距缩至 4.5μm

发布于2026-04-30 阅读(0)

发布于2026-04-30 阅读(0)

扫一扫,手机访问

台积电更新SoIC 3D芯片封装堆叠技术路线图:2029年互连间距缩至4.5μm

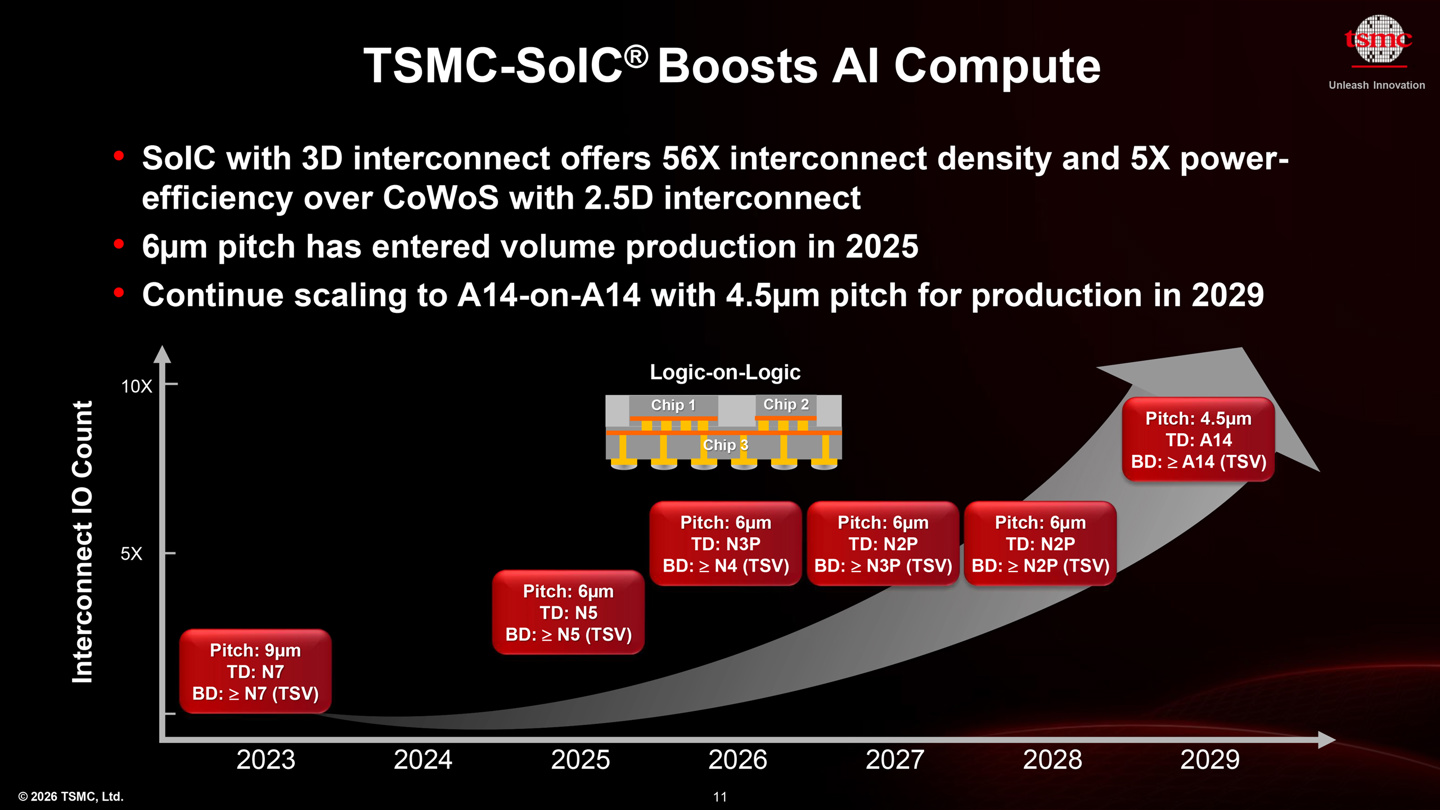

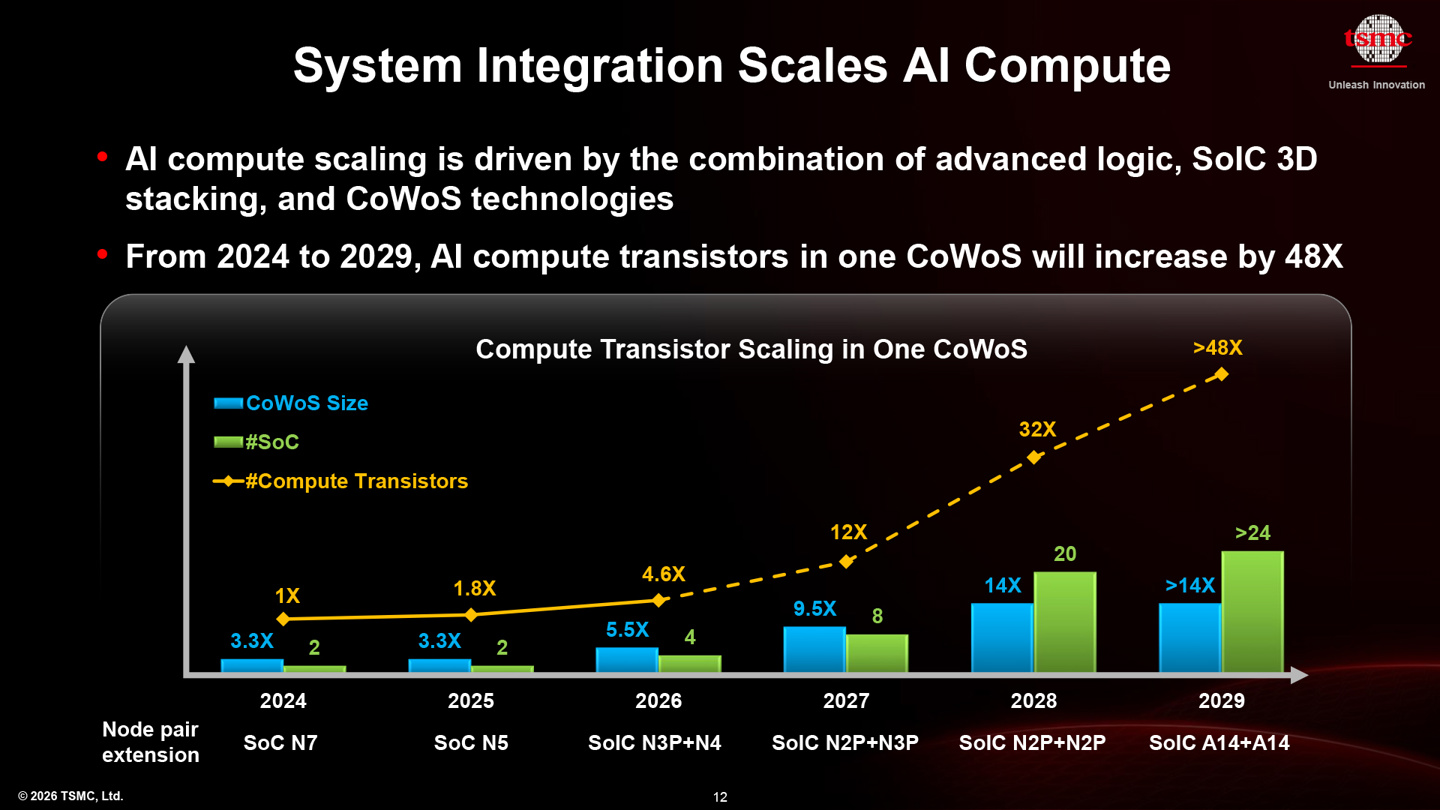

近期,在北美的一场技术研讨会上,台积电更新了其SoIC 3D堆叠技术的路线图,为未来几年的技术演进指明了方向。其中一项核心目标,是计划将现有的6μm互连间距进一步微缩,预计到2029年将缩小至4.5μm。

这里需要先明确一下,SoIC全称为System on Integrated Chips,是台积电自主研发的一项3D IC封装技术。它的核心在于,能够将多个芯片进行垂直堆叠,从而实现更高性能与更高密度的集成。

那么,它与传统封装技术有何不同?关键在于“直接互连”。SoIC利用先进的混合键合技术,让芯片与芯片之间的金属层直接“对话”,这大幅缩短了信号传输的路径。带来的好处显而易见:功耗更低,延迟更小。正因如此,这项技术尤其受到高性能计算和AI芯片领域的青睐。

技术路径:面对面与背对背的差异

深入技术细节,SoIC主要分为两种堆叠方式:Face-to-Back(F2B,背对背)和 Face-to-Face(F2F,面对面)。这两种方式的性能表现,可谓天差地别。

先看F2B方式。由于其物理结构的限制,信号必须穿过底部芯片的硅通孔(TSV)以及多层金属布线才能到达上层芯片。这个过程不仅增加了额外的延迟和功耗,更关键的是,它从根本上限制了互连的密度。数据显示,采用F2B设计的信号密度大约在1500个/mm²。

相比之下,F2F方式则采用了更为直接的思路。它通过混合铜键合技术,将两块芯片的金属层面对面地连接起来,完全绕开了TSV。这种“直连”模式带来了质的飞跃——信号密度飙升至约14000个/mm²。这意味着芯片间的通信效率极高,几乎接近了单颗芯片内部互连的水平。

路线图演进:从9μm走向4.5μm

互连间距的微缩,是衡量这项技术精密度与先进性的关键标尺。回顾一下进程:台积电在2023年已经实现了9µm的互连间距,这个精度已经相当惊人,足以支撑像AMD Instinct MI300系列这样的高端产品。不过,当时的第一代SoIC技术仅支持F2B设计。

而根据最新的路线图,台积电计划在2025年将互连间距缩短到6μm。这还不是终点,他们的目光放得更远,预估到2029年,这一间距将进一步微缩至4.5µm。每一次微缩,都意味着集成密度和性能的又一次提升。

落地应用:富士通Monaka处理器的实践

技术路线再宏伟,也需要实际产品的验证。目前,富士通的Monaka处理器成为了SoIC技术首个重量级的应用案例。这款面向数据中心的CPU拥有144个Armv9核心,其设计颇具巧思:计算模块采用台积电最先进的N2工艺制造,然后通过前述的F2F方式,堆叠在由N5工艺制造的SRAM芯片之上。这种异构集成与3D堆叠的结合,正是未来高性能芯片设计的一个重要方向。

免责声明:正软商城发布此文仅为传递信息,不代表正软商城认同其观点或证实其描述。

产品推荐

-

售后无忧

立即购买>- DAEMON Tools Lite 10【序列号终身授权 + 中文版 + Win】

-

¥150.00

office旗舰店

-

售后无忧

立即购买>- DAEMON Tools Ultra 5【序列号终身授权 + 中文版 + Win】

-

¥198.00

office旗舰店

-

售后无忧

立即购买>- DAEMON Tools Pro 8【序列号终身授权 + 中文版 + Win】

-

¥189.00

office旗舰店

-

售后无忧

立即购买>- CorelDRAW X8 简体中文【标准版 + Win】

-

¥1788.00

office旗舰店

-

正版软件

正版软件

- 美股异动|芯片存储板块盘前普跌 西部数据跌超7%

- 西部数据盘前重挫,存储芯片板块承压 市场情绪这东西,有时候真像六月的天。你看,这边厢业绩指引明明大幅超出了预期,那边厢股价却应声下跌。今天盘前,存储芯片板块就上演了这么一出。 具体来看,西部数据(Western Digital)盘前跌幅超过了7%,领跌板块。其同门兄弟闪迪(SanDisk)的跌幅也超

- 20小时前 20:36 0

-

正版软件

正版软件

- 小米重磅新品!二代电竞鼠标来了 性价比或将再升级

- 小米电竞鼠标2官宣:旗舰传感器+主控,轻量化设计能否延续? 昨天,小米正式揭开了“小米电竞鼠标2”的面纱。根据官方信息,这款新品将搭载旗舰级传感器、旗舰级主控,并经过电竞级调校,硬件堆料可谓直接拉满。 消息一出,迅速引发了外媒的关注。vgtimes就发文分析了这款鼠标的潜在升级方向。从目前公布的资料

- 21小时前 20:04 0

-

正版软件

正版软件

- 小米汽车:4月交付量超30000台

- 小米汽车:4月交付量超30000台 市场传来最新动态。2026年4月,小米汽车的月度交付量正式突破了30000台大关。这个数字,无疑为新能源汽车市场的竞争格局,投下了一枚分量不轻的砝码。 从零到月交付三万,这不仅仅是产能爬坡的胜利,更是一个新品牌在激烈市场中站稳脚跟的关键信号。回顾其交付曲线,能够清

- 22小时前 19:02 0

-

正版软件

正版软件

- 联想 Think Book 14+/16+ 2026 笔记本锐龙款新增 AI 7 H 450 处理器版,32GB+1TB 版售 6999 元

- 嘿,各位关注笔记本动态的朋友们!刚刚得到消息,联想ThinkBook 14+和16+的2026款现在终于迎来了锐龙版本。这两款机型分别配备了14.5英寸和16英寸的屏幕,都搭载了备受关注的锐龙AI 7 H 450处理器,还配备了ForcePad压感触控板这个亮点功能。最让人惊喜的是,32GB+1TB

- 昨天 05-01 16:26 0

-

正版软件

正版软件

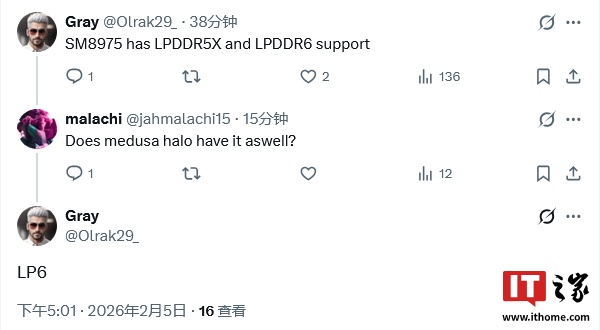

- AMD "Medusa Halo" 处理器被曝将支持 LPDDR6 内存

- AMD下一代重磅冲击波:代号“Medusa Halo”的处理器或将率先拥抱LPDDR6内存 话说回来,最近关于AMD下一代处理器的消息真是越来越密集了。就在不久前,知名爆料人Gray(在X平台上的账号是@Olrak29_)又扔下了一个新“瓜”。他透露,AMD基于“Zen 6”架构、面向高端锐龙AI

- 昨天 05-01 16:25 0

最新发布

-

1

1

- 在哪里可以找到手机相片收藏

- 525天前

-

2

2

- 详细解读I7-14650HX的性能评测数据

- 532天前

-

3

3

- 如何选择DP接口版本: 1.2还是1.4?

- 543天前

-

4

4

-

5

5

- 华为GT4和Watch4,哪个更好?

- 835天前

-

6

6

- 骁龙芯片的型号与天玑9400相当?

- 551天前

-

7

7

-

8

8

-

9

9

- 三星“约谈”联发科 A系列智能手机有望搭载其5G芯片

- 2329天前

相关推荐

- 美股异动|芯片存储板块盘前普跌 西部数据跌超7%

- 小米重磅新品!二代电竞鼠标来了 性价比或将再升级

- 小米汽车:4月交付量超30000台

- 联想 Think Book 14+/16+ 2026 笔记本锐龙款新增 AI 7 H 450 处理器版,32GB+1TB 版售 6999 元

- AMD "Medusa Halo" 处理器被曝将支持 LPDDR6 内存

- 英特尔代码补丁显示 "Nova Lake P" 处理器核显搭载 Xe3p_LPG 图形引擎

- 2026 款联想 ThinkBook 14/16 锐龙版笔记本首销:R7 H 260 处理器,24G +1T 售 5599 元 / 5699 元

- 联想 ThinkBook 14/16 2026 锐龙版开启新品预约:R7 H 260 处理器,24GB+1TB 版 5599 元 / 5699 元

- TUXEDO 推出英特尔版 InfinityBook Max 15 Gen10 笔记本:可选 255H + 5070

热门关注

-

- Xshell 6 简体中文

- ¥899.00-¥1149.00

-

- DaVinci Resolve Studio 16 简体中文

- ¥2550.00-¥2550.00

-

- Camtasia 2019 简体中文

- ¥689.00-¥689.00

-

- Luminar 3 简体中文

- ¥288.00-¥288.00

-

- Apowersoft 录屏王 简体中文

- ¥129.00-¥339.00