台积电更新SoIC 3D堆叠技术路线图:2029年互连间距缩至4.5μm

发布于2026-04-30 阅读(0)

发布于2026-04-30 阅读(0)

扫一扫,手机访问

台积电更新SoIC路线图:互连间距持续微缩,2029年瞄准4.5µm

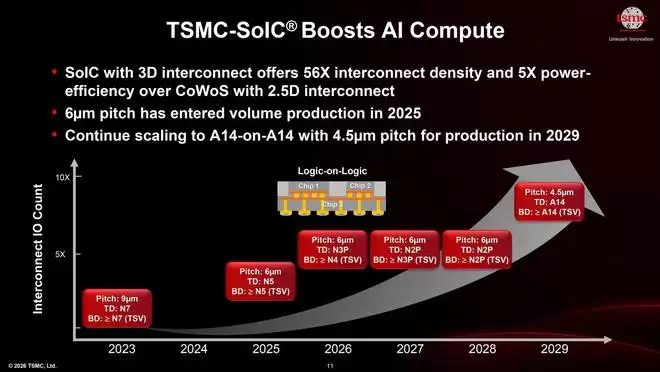

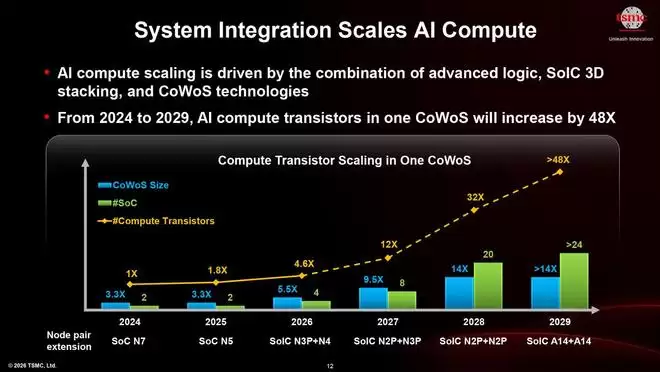

最近,台积电在北美的一场技术研讨会上,更新了其SoIC 3D堆叠技术的路线图,为未来几年的技术演进划定了清晰的路径。其中最关键的一个目标,就是持续缩小芯片间的互连间距——计划从现有的6µm起步,一路推进,目标是在2029年达到4.5µm。

这里先简单解释一下,SoIC的全称是System on Integrated Chips。这是台积电自主研发的一套3D IC封装技术,核心思路就是把多个芯片像搭积木一样垂直堆叠起来,从而实现更高性能、更高密度的系统集成。

那么,它比传统封装强在哪儿呢?关键在于“直接连接”。SoIC采用了混合键合技术,让芯片之间能够实现直接的电气互连。这带来的好处显而易见:信号传输的路径被大幅缩短,随之而来的就是功耗和延迟的显著降低。正因如此,这项技术尤其受高性能计算和AI芯片的青睐。

具体到技术实现路径,SoIC主要有两种堆叠方式:Face-to-Back(F2B,背对背)和Face-to-Face(F2F,面对面)。这两种方式的性能差异,可以说是一个天上一个地下。

F2B结构存在天然的物理限制。信号想要从上芯片传到下芯片,必须穿过底部的硅通孔(TSV)以及多层金属布线。这个过程不仅增加了延迟和功耗,更关键的是,它严重限制了互连的密度。有数据显示,采用F2B设计的信号密度大约只有1500个/mm²。

而F2F方案就完全是另一番景象了。它通过混合铜键合技术,直接将两块芯片的金属层面对面连接起来,完全绕开了TSV。这样一来,信号密度实现了数量级的飞跃,飙升至14000个/mm²。这意味着,芯片之间的通信性能几乎可以媲美芯片内部互连的水平,瓶颈被极大地打破。

话说回来,如果我们聚焦到最直观的互连间距指标,就能看到台积电清晰的推进节奏。早在2024年,台积电就已经实现了9µm的精细间距,这个水平已经足以支撑像AMD Instinct MI300系列这样的高端产品了。不过,当时的第一代SoIC还只支持F2B设计。

接下来的路线图非常明确:2025年,互连间距将缩小到6µm。而这还不是终点,按照台积电的预估,到2029年,这一关键尺寸将进一步微缩至4.5µm。持续的微缩,意味着更密的互连、更高的带宽和更强的整体性能,这无疑是面向未来算力需求的关键布局。

免责声明:正软商城发布此文仅为传递信息,不代表正软商城认同其观点或证实其描述。

产品推荐

-

售后无忧

立即购买>- DAEMON Tools Lite 10【序列号终身授权 + 中文版 + Win】

-

¥150.00

office旗舰店

-

售后无忧

立即购买>- DAEMON Tools Ultra 5【序列号终身授权 + 中文版 + Win】

-

¥198.00

office旗舰店

-

售后无忧

立即购买>- DAEMON Tools Pro 8【序列号终身授权 + 中文版 + Win】

-

¥189.00

office旗舰店

-

售后无忧

立即购买>- CorelDRAW X8 简体中文【标准版 + Win】

-

¥1788.00

office旗舰店

-

正版软件

正版软件

- 消息称 TOP5 手机厂商有 3 家在做 Pocket 类影像产品,还有子系品牌在计划掌机类产品

- 行业动态:手机巨头的新赛道 内存价格持续走高,这事儿对手机厂商的影响,远比想象中要大。最近圈内传出的风声显示,单纯依靠手机硬扛成本压力已经不够看了,头部玩家们正忙着开辟新战场。 有可靠消息指出,全球前五的手机厂商中,已经有三位在悄悄布局“Pocket”类的便携影像产品。看来,运动相机、手持云台这个市

- 6分钟前 0

-

正版软件

正版软件

- 致敬经典 Commodore 64,八位堂推出 Retro R8 鼠标 - C64 版

- 致敬经典 Commodore 64,八位堂推出 Retro R8 鼠标 在科技产品的历史长廊里,总有一些设计能瞬间将我们拉回某个黄金年代。这不,八位堂近期推出的Retro R8鼠标C64版,就精准复刻了上世纪80年代的经典风潮——它致敬的对象,正是吉尼斯世界纪录认证的、史上最畅销的单型号电脑:Com

- 7分钟前 0

-

正版软件

正版软件

- 华硕 ROG STRIX B850-A GAMING WIFI7 S NEO 吹雪主板开启预约,2199 元

- 华硕ROG B850吹雪主板开启预约:2199元,白色美学与硬核配置的又一次融合 市场预热了一段时间后,华硕旗下融合了“雪武战姬”IP的吹雪系列新作,终于确定了型号和价格。没错,就是之前大家猜测的ROG STRIX B850-A GAMING WIFI7 S NEO。目前这款主板已经开启预约,标价2

- 8分钟前 0

-

正版软件

正版软件

- 一波Intel 18A酷睿处理器新机上市 开启端侧AI新体验

- 当下,一个信号正在技术演进中浮现 技术圈正在发生一个有趣的转变:围绕AIAgent的探索不再局限于少数极客的试验场,而是开始吸引更广泛群体的积极参与。这股“数字员工”的热潮可谓席卷全网——从自主规划差旅行程到智能撰写工作周报,AI正从单纯的“对话助手”升级为能实际解决问题的“数字打工人”。越来越多职

- 20分钟前 0

-

正版软件

正版软件

- 最容易维修的苹果本!MacBook Neo仅需6分钟拆解:模块化设计 键盘可单独更换

- 苹果MacBook Neo开售:维修友好度创历史新高 最新消息显示,苹果MacBook Neo已于近日正式发售。经过各类补贴与优惠叠加后,国行版本实际到手价约3000元,在苹果产品线中展现出难得的性价比优势。 更值得关注的是,这款产品不仅刷新了苹果笔记本的价格下限,更在可维修性方面实现了重大突破。

- 20分钟前 0

最新发布

-

1

1

- 在哪里可以找到手机相片收藏

- 523天前

-

2

2

- 详细解读I7-14650HX的性能评测数据

- 530天前

-

3

3

- 如何选择DP接口版本: 1.2还是1.4?

- 541天前

-

4

4

-

5

5

- 华为GT4和Watch4,哪个更好?

- 833天前

-

6

6

- 骁龙芯片的型号与天玑9400相当?

- 549天前

-

7

7

-

8

8

-

9

9

- 三星“约谈”联发科 A系列智能手机有望搭载其5G芯片

- 2327天前

相关推荐

- 配件厂商 Plugable 回应兼容苹果 MacBook Neo 情况:双头 USB-C 扩展坞恐降速

- 安克智能盾 10000mAh 移动电源首销:有线 27W + 无线 7.5W,349 元

- 七彩虹公布首款 BTF 3.0 背插主板更多细节:长于标准 M-ATX

- 消息称某厂中端新机配备 6.59 英寸直屏 + 天玑 8500 处理器,预计为小米旗下

- 酷比魔方掌玩 mini 4 Ultra 平板完整规格曝光:天玑 8300 处理器、7200mAh 电池、开放 BL 解锁

- 消息称 TOP5 手机厂商有 3 家在做 Pocket 类影像产品,还有子系品牌在计划掌机类产品

- 致敬经典 Commodore 64,八位堂推出 Retro R8 鼠标 - C64 版

- 华硕 ROG STRIX B850-A GAMING WIFI7 S NEO 吹雪主板开启预约,2199 元

- 一波Intel 18A酷睿处理器新机上市 开启端侧AI新体验

热门关注

-

- Xshell 6 简体中文

- ¥899.00-¥1149.00

-

- DaVinci Resolve Studio 16 简体中文

- ¥2550.00-¥2550.00

-

- Camtasia 2019 简体中文

- ¥689.00-¥689.00

-

- Luminar 3 简体中文

- ¥288.00-¥288.00

-

- Apowersoft 录屏王 简体中文

- ¥129.00-¥339.00