4F Square架构全球首发三星实现10纳米DRAM技术突破

发布于2026-04-26 阅读(0)

发布于2026-04-26 阅读(0)

扫一扫,手机访问

三星取得关键突破:4F Square与VCT技术助力10a DRAM迈向2028年量产

近日,行业传来重磅消息。根据韩媒The Elec于4月24日的报道,三星电子在下一代DRAM技术的研发上取得了实质性进展——他们已经成功生产出采用革命性的4F Square单元结构与垂直通道晶体管(VCT)技术的10a DRAM晶圆,测试中已确认功能性芯片,并计划于2028年实现量产。

这意味着什么?简单来说,这标志着业界首次将这两项关键技术从蓝图变为现实,并整合进DRAM的生产流程。它为突破当前的内存微缩瓶颈,打开了一扇新的大门。

技术基石:什么是4F Square与VCT?

要理解这次突破的价值,得先弄清楚这两个核心概念。

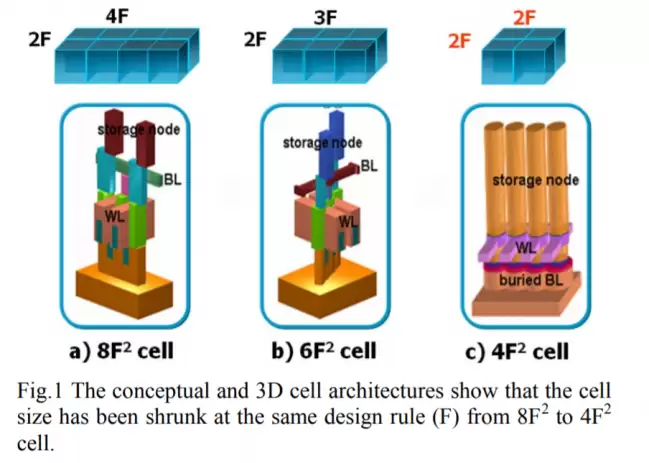

先说4F Square单元结构。这里的“F”指的是光刻工艺的最小特征尺寸。你可以把它想象成规划存储单元的“地基”标准。传统的设计是6F Square,而4F Square则将每个存储单元压缩在2F×2F的面积内。结果显而易见:在同样大小的芯片“地盘”上,能盖起更多、更密集的“存储单元大楼”,从而显著提升存储密度。这无疑是实现DRAM高密度微缩的一条关键路径。

然而,光有紧凑的“地基规划”还不够,还得有新的“建筑工艺”来实现它。这就是垂直通道晶体管(VCT)登场的原因。顾名思义,VCT将晶体管的通道方向从传统的“平躺”(水平)改为“站立”(垂直)。这一改变带来了一个绝妙的好处:电荷存储电容可以直接堆叠在晶体管的上方,形成立体结构。

这就好比从平房改建为楼房,极大地缩短了单元之间的“邻里间距”,有效打破了传统平面结构在微缩道路上的物理极限。可以说,VCT技术正是实现4F Square那种超高密度单元布局的物理基础。

目标与挑战:10a节点的飞跃与材料攻坚战

那么,这套组合拳瞄准的是哪个目标节点?答案是:10a工艺。在DRAM的技术路线图中,10a被视为进入10纳米以下时代的首代技术,其实际电路线宽大约在9.5至9.7纳米之间。根据估算,相比当前主流的6F Square设计,4F Square结构有望在相同芯片面积下,将单元密度提升约30%到50%。这是一个相当可观的性能飞跃。

当然,通往量产的道路从来都不是一帆风顺的,尤其是当技术架构发生根本性变革时。目前,主要的挑战集中在材料领域。

为了降低漏电流并提升数据保持能力,晶体管的通道材料已经从硅转向了铟镓锌氧化物(IGZO)。这本身就是一个重要的材料切换。此外,在字线(用于寻址存储单元的导线)材料上,三星原计划用钼(Mo)来替代传统的氮化钛(TiN),以期获得更好的电学性能。

但问题在于,钼材料具有腐蚀性,且在固态处理上较为困难,需要对现有的气体输送系统进行改造。因此,这项材料的替换方案目前仍处于评估阶段。如何攻克这些材料工艺的难关,将是决定10a DRAM能否如期、稳定量产的关键因素之一。

总而言之,三星此次成功产出功能性晶圆,无疑为行业注入了一剂强心针。它证明了4F Square与VCT技术路线的可行性,并将下一代DRAM的竞争赛道,清晰地指向了2028年这个时间窗口。接下来的几年,将是技术优化与量产攻坚的深水区,值得持续关注。

免责声明:正软商城发布此文仅为传递信息,不代表正软商城认同其观点或证实其描述。

产品推荐

-

售后无忧

立即购买>- DAEMON Tools Lite 10【序列号终身授权 + 中文版 + Win】

-

¥150.00

office旗舰店

-

售后无忧

立即购买>- DAEMON Tools Ultra 5【序列号终身授权 + 中文版 + Win】

-

¥198.00

office旗舰店

-

售后无忧

立即购买>- DAEMON Tools Pro 8【序列号终身授权 + 中文版 + Win】

-

¥189.00

office旗舰店

-

售后无忧

立即购买>- CorelDRAW X8 简体中文【标准版 + Win】

-

¥1788.00

office旗舰店

-

正版软件

正版软件

- 7月25日外媒科学网站摘要:科学家警告,人类正无意间向宇宙泄露“地球坐标”

- 《自然》:一桩悬案了结? “砷基生命”论文终遭撤稿,但争议远未结束 科学界一桩持续了15年的公案,最近有了新进展。顶级期刊《科学》(Science)正式撤回了那篇曾引发轰动的争议性论文——该研究当年声称,在美国加州莫诺湖发现的一种细菌,能够用有毒的砷元素替代生命必需的磷来构建DNA,这直接挑战了我们

- 10分钟前 0

-

正版软件

正版软件

- 马斯克的火箭炸了,碎片掉进邻国,墨西哥称已遭污染,正考虑起诉SpaceX

- SpaceX星舰爆炸残骸回收遇阻,向墨西哥寻求协助 事情有了新进展。根据路透社6月27日的报道,SpaceX在周四对外透露,上周星舰(Starship)发生爆炸后,其残骸回收工作遇到了麻烦。目前,公司已经向墨西哥方面寻求合作。值得注意的是,墨西哥总统此前曾公开表示,不排除对SpaceX采取法律行动的

- 11分钟前 0

-

正版软件

正版软件

- 下调降至150万颗!HBM4验证延迟拖累英伟达Rubin GPU量产

- 英伟达Rubin GPU量产进度调整,HBM4验证成关键变量 最近供应链传来消息,英伟达备受瞩目的下一代Rubin GPU,量产节奏可能要比预期慢上半拍。根据最新信息,其生产目标已从原先的200万颗下调至150万颗左右。这背后,下一代高带宽内存HBM4的验证进度,成了眼下最主要的制约因素。 产能布局

- 11分钟前 0

-

正版软件

正版软件

- 北京信息光电子芯片平台预计今年6月产线贯通

- 北京信息光电子芯片平台迈入关键阶段,核心设备正式入驻 近日,从北京经济技术开发区传来新进展。3月31日,北京信息光电子芯片平台的首批核心设备,正式搬入位于北京亦庄之所新质产业园的厂房。这可不是简单的设备进场,它标志着一个关键转折——平台建设自此告别了基础设施建设阶段,全面转入设备安装与调试的新征程。

- 13分钟前 0

-

正版软件

正版软件

- 骁龙新芯曝16MB共享L2,规格够猛

- 骁龙新旗舰芯片规格曝光:L2缓存激进,GPU配置亮眼 关于高通下一代旗舰移动平台的消息,最近又有了新动静。知名数码博主 @数码闲聊站 在微博上透露了一组关键信息,让这款代号为“SM8975”的芯片轮廓逐渐清晰。 骁龙 8 Elite Gen6 Pro (SM8975) 疑似共享 16MB L2;8M

- 13分钟前 0

最新发布

-

1

1

- 在哪里可以找到手机相片收藏

- 519天前

-

2

2

- 详细解读I7-14650HX的性能评测数据

- 526天前

-

3

3

- 如何选择DP接口版本: 1.2还是1.4?

- 537天前

-

4

4

-

5

5

- 华为GT4和Watch4,哪个更好?

- 829天前

-

6

6

- 骁龙芯片的型号与天玑9400相当?

- 545天前

-

7

7

-

8

8

-

9

9

- 三星“约谈”联发科 A系列智能手机有望搭载其5G芯片

- 2323天前

相关推荐

热门关注

-

- Xshell 6 简体中文

- ¥899.00-¥1149.00

-

- DaVinci Resolve Studio 16 简体中文

- ¥2550.00-¥2550.00

-

- Camtasia 2019 简体中文

- ¥689.00-¥689.00

-

- Luminar 3 简体中文

- ¥288.00-¥288.00

-

- Apowersoft 录屏王 简体中文

- ¥129.00-¥339.00